Beschreibung der Jumper

Beschreibung der Jumper

(gültig ab Platinenversion V2)

JP1 -

Anstelle der CR2032 kann hier eine externe Batterie angeschlossen werden. Die Spannung darf nicht höher sein als die Betriebsspannung des Rechners, also maximal 5V. Die Untergrenze wird durch den auf Sockel Nr.5 gesteckten RAM bestimmt (Spannungsabfall über D1 beachten!). Siehe auch Abschnitt "Batteriebackup" in Hardwareaufbau.

JP2/JP3/JP4 -

Ist auf den Typ des im zugehörigen Sockel bestückten Speichers (RAM oder ROM) einzustellen. Fehlstellung führt bei RAM zu Nichtbeschreibbarkeit und kann bei ROM den Verlust oder die Beschädigung des Inhaltes zur Folge haben. Siehe auch Abschnitt Speicherbestückung in der Dokumentation.

JP5 -

Ist abhängig von der Größe des in Sockel 1 bestückten ROMs einzustellen.

Position "16" -

Position "32/64" -

Verbindet Pin 23 des Sockels 1 in Stellung "16" mit Vcc und in Stellung "32/64" mit A11. Fehlstellung führt bei 4Kx8 oder 8Kx8 ROMs zu Adressierungsfehlern und kann bei 2Kx8 ROMs den Verlust oder die Beschädigung des Inhaltes zur Folge haben. Siehe auch Abschnitt Speicherbestückung in der Dokumentation.

JP6 (siehe weiter unten)

JP7 -

Mit diesem Jumper kann bestimmt werden, ob die internen RAM-

JP8 -

Dieser Jumper muß gesetzt werden, wenn die SIO nicht bestückt ist. Er überbrückt

die ansonsten offene Hardware-

JP9 -

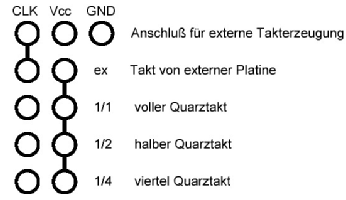

Stellt das Teilerverhältnis zwischen Quarz und Systemclock ein und ist gleichzeitig Connector für die optionale externe Takterzeugung.

JP10 -

Anschluß für die Tastatur. Die Belegung der Pins wird ausführlich im Abschnitt "Tastatur" der Dokumentation erklärt.

JP11 -

Anschluß für den alternativen Lautsprecher.

JP12 -

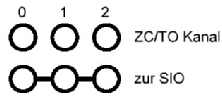

Schaltet den gewünschten CTC-

JP13 -

(ab Platinenversion V2 vorhanden)

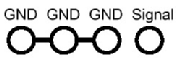

Stellt Abgriffe der CTC Ein-

JP14 -

(ab Platinenversion V3 vorhanden)

Dient dem schnellen Abtrennen des Lautsprechers, wenn kein Tonsignal gewünscht ist. Im Normalzustand gesteckt.

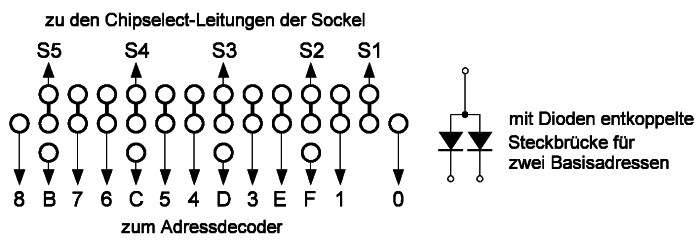

JP6 -

(Layout gültig ab Platinenversion V2)

Verbindet die Chipselectleitungen der Sockel 1-

Hinweis: Die Decoderausgänge "9" und "A" sind nicht auf JP6 herausgeführt, können bei Bedarf jedoch direkt am IC AD3 abgegriffen werden (Stiftleiste bestücken).

Die Adressdecodierung des LC80ex arbeitet in Schritten von 4KB. Um bei 8Kx8 Speichern

die volle Größe nutzen zu können, müssen diesen daher zwei Basisadressen zugewiesen

werden. Weil die Adressdecoder jedoch keine Opendrain-

Bei der Zuweisung der Basiadressen zu 8Kx8 Speichern muß eine weitere Besonderheit beachtet werden. Da die Adressleitung A12 bestimmt, ob die oberen oder unteren 4K angesprochen werden, treten zwei Effekte auf. Erstens können nicht zwei gerade oder zwei ungerade Adressen kombiniert werden, sonst wird immer nur eine Hälfte aktiv. Es muß immer eine ungerade mit einer geraden Adresse gepaart werden. Und zweitens muß die Reihenfolge beim Brennen von ROMs beachtet werden. Gerade Basisadressen (z.B. 0000H, 4000H, A000H) sprechen immer die unteren 4K an und ungerade (z.B. 1000H, 5000H, B000H) die oberen 4K.

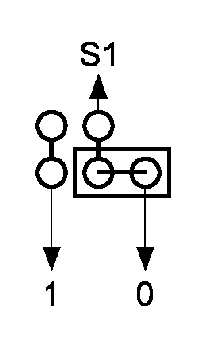

Beispiel 1:

Einem 2716 ROM auf Sockel 1 soll die Basisadresse 0000H zugewiesen werden. Dazu einfache Jumperbrücke zwischen "S1" und "0" stecken. (linkes Bild)

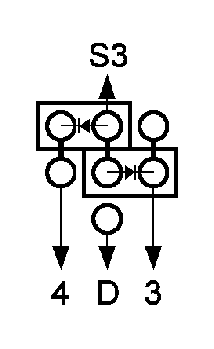

Beispiel 2:

Einem 6264 RAM auf Sockel 3 sollen die Basisadressen 3000H und 4000H zugewiesen werden. Dazu diodenentkoppelte Jumperbrücken mit den Anoden an "S3" und den Kathoden an "3" bzw. "4" setzen. (rechtes Bild)